实验3 Tomasulo算法

1 实验目的

(1) 加深对指令级并行性及开发的理解。

(2) 加深对Tomasulo算法的理解。

(3) 掌握Tomasulo算法在指令流出、执行、写结果各阶段对浮点操作指令以及load和store指令进行了什么处理。

(4) 掌握采用了Tomasulo算法的浮点处理部件的结构。

(5) 掌握保留站的结构。

(6) 给定被执行的程序片段,对于具体某个时钟周期,能够写出保留站、指令状态表以及浮点寄存器状态表内容的变化情况。

2 实验平台

采用Tomasulo算法模拟器。

3 实验内容和步骤

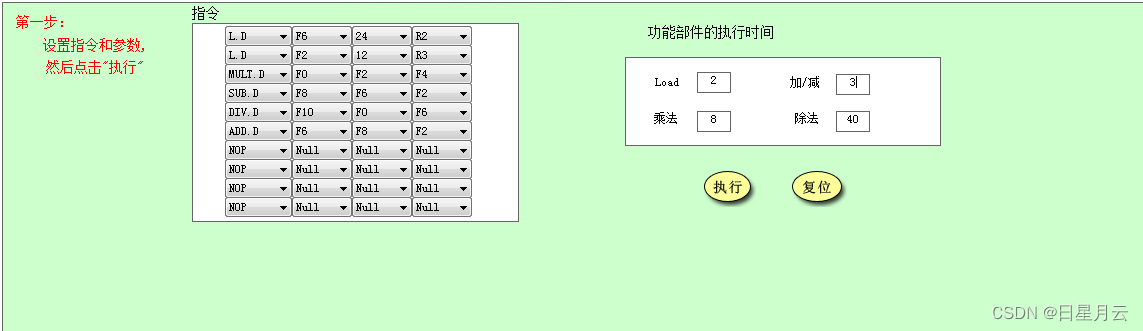

首先要掌握Tomasulo算法模拟器的使用方法(见随附的ppt)。

1)、假设浮点功能部件的延迟时间为:加减法2个时钟周期,乘法10个时钟周期,除法40个时钟周期,Load部件2个时钟周期。

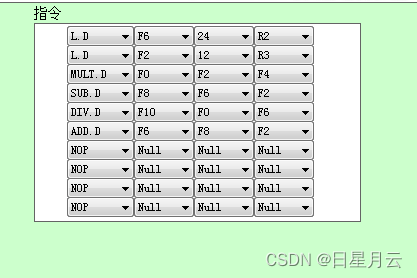

(1) 对于下面的代码段,给出当指令MUL.D写结果时,保留站、Load缓冲器以及寄存器状态表中的内容。

L.D F6,24(R2)

L.D F2,12(R3)

MUL.D F0,F2,F4

SUB.D F8,F6,F2

DIV.D F10,F0,F6

ADD.D F6,F8,F2

(2) 按单步方式执行上述代码,利用模拟器的对比显示功能,观察每一个时钟周期前后各信息表中内容的变化情况。

2)、对于上面相同的延迟时间和代码段:

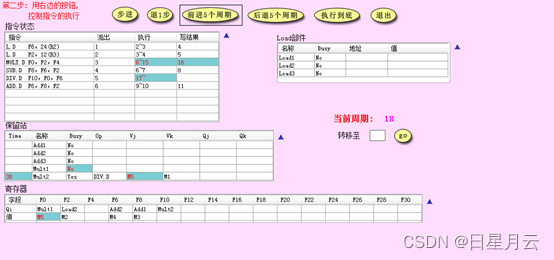

(1) 给出在第3个时钟周期时,保留站、Load缓冲器以及寄存器状态表中的内容。

可以看到

保留站中Multi的Qj字段是Load2,寄存器换名技术,存储到保留站

寄存器中F2的Qi是Load2

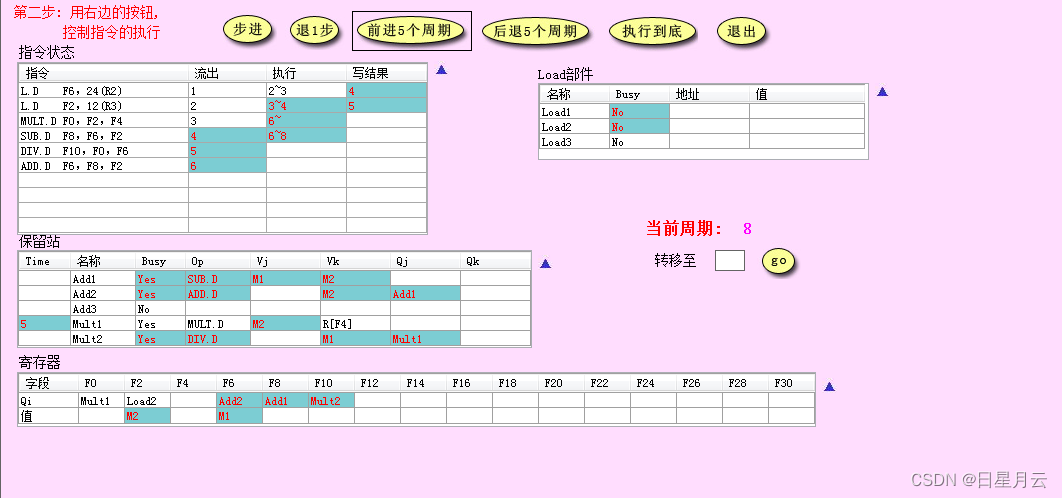

(2) 步进5个时钟周期,给出此时保留站、Load缓冲器以及寄存器状态表中的内容。

可以看到

ADD2的Vj是M3(F8),Vk是M2(F2)

Mult1的Vj是M2(F2),Vk是R[F4]

Mult2的Vk是M1(F6),Qj是Mult1(运算后的F0)

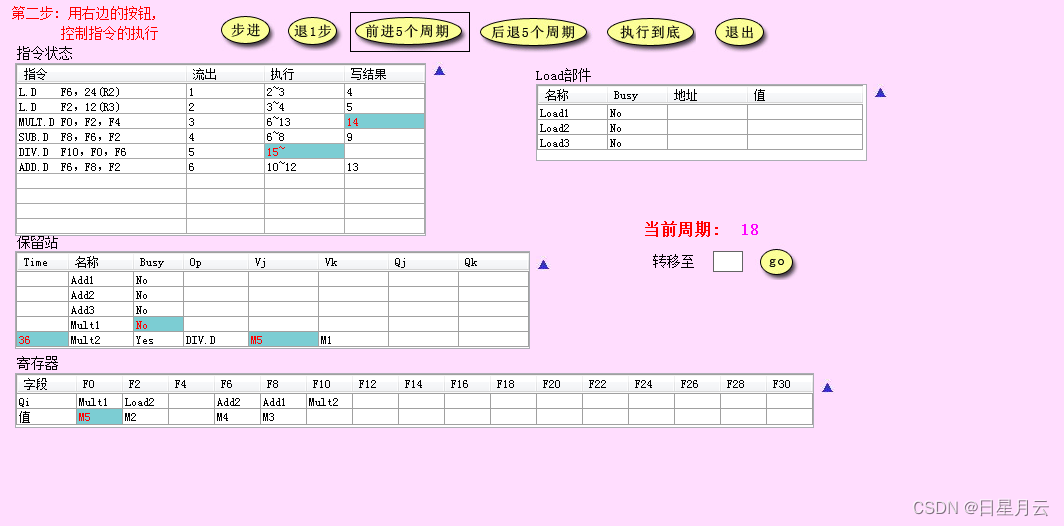

再步进10个时钟周期,给出此时保留站、Load缓冲器以及寄存器状态表中的内容。

可以看出

Mutl2的Vj是M5(F0),Vk是M1(F6)

3)、假设浮点功能部件的延迟时间为:加减法3个时钟周期,乘法8个时钟周期,除法40个时钟周期,自己编写一段程序,重复上述步骤(2)的工作。并给出通过此项工作,得出什么结论?

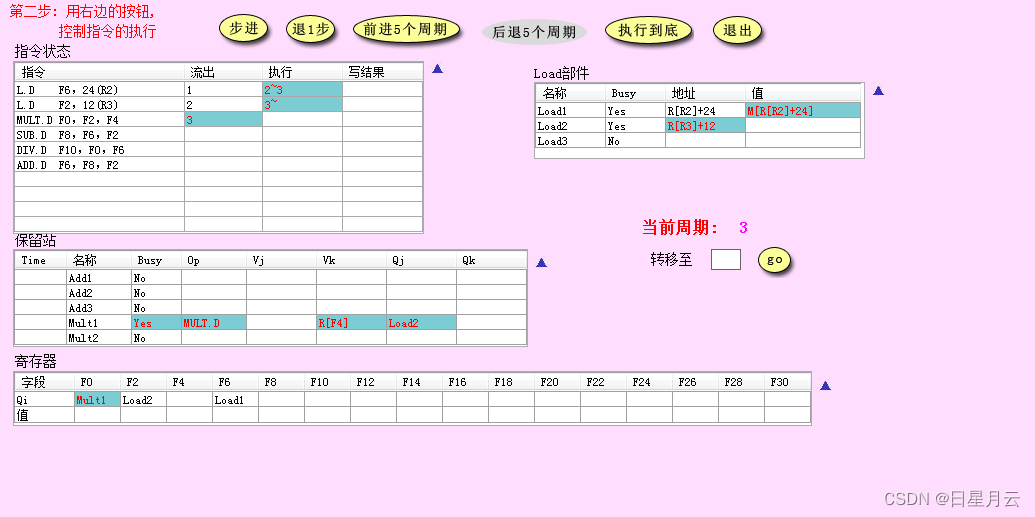

(1) 给出在第3个时钟周期时,保留站、Load缓冲器以及寄存器状态表中的内容。

可以看到

Mutl1的Vk是R[F4],Qj是Load2(F2)

(2) 步进5个时钟周期,给出此时保留站、Load缓冲器以及寄存器状态表中的内容。

可以看到

ADD1的Vj是M1(F6),Vk是M2(F2)

ADD2的Qj是Add1(F8),Vk是M2(F2)

Mult1的Vj是M2(F2),Vk是R[F4]

Mult2的Vk是M1(F6),Qj是Mult1(运算后的F0)

(3) 再步进10个时钟周期,给出此时保留站、Load缓冲器以及寄存器状态表中的内容。

可以看出

Mutl2的Vj是M3(F0),Vk是M1(F6)

4 实验总结与心得

Tomasulo算法的核心思想:

- 记录和检测指令相关,操作数一旦就绪就立即执行,把发生RAM冲突的减小到最少。

- 通过寄存器换名来消除WAR冲突和WAW冲突。

Tomasulo算法的基本结构

- 见 课本 图4.1

Tomasulo具体算法

(1) 指令流出

(2) load和store指令

(3) 写结果