在当前大数据网络环境下,基于FPGA的云主机技术对单FPGA板卡实现PCIe PF和PCIe VF的规模以及更新的灵活度有更高的需求,而当前技术中PCIe PF和PCIe VF规模受限于FPGA资源,扩展难度大,迭代周期长。本文提出将Host的PCIe PF和PCIe VF枚举过程的交互由SOC来实现,FPGA仅透传相关的配置包,从而达到可灵活扩展PCIe PF和PCIe VF规模的目标,同时FPGA资源可以更有效的专注于数据通道的加速。

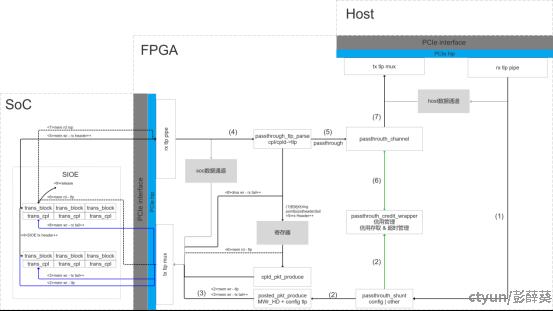

在该架构中,管理软件运行在SoC上,用于实现PCIe PF和PCIe VF的配置。Host通过PCIe接口检测FPGA板卡,FPGA将config tlp包透传至SoC,由SoC来实际处理枚举流程,FPGA负责Host和SoC之间的包传输。由于SoC的软件更新更灵活,资源比FPGA更丰富,使得该方案可以更灵活的扩充PCIe PF和PCIe VF,更好的应用于当前大数据背景。图一是系统架构图。

图一 系统架构图

该方案的核心在于FPGA透传通道将Host下发的完整的config tlp包作为payload封装成一个Memory Write的tlp包写入SoC内存,SoC解析该tlp包并完成相关处理后,将需要返回Host的tlp包存入另一块内存空间并通知FPGA,FPGA读回该tlp包并将其转为CPL或者CPLD包返回给Host侧,这样就完成了一次Host和SoC之间的数据交互。多次重复直至完成一个完整的枚举流程,SoC将最终的配置结果下发给FPGA,用于后续数据通道的处理。透传通道完成一次完整的Host和SoC的数据交互流程如下:

(1)FPGA对Host侧rx方向的tlp包进行分流,控制通道的包进入透传通道;

(2)控制通道分流,并将相关信息进行信用存取;

(3)完整的config tlp包作为payload封装成一个Memory Write的tlp包写入SoC内存;

(4)SoC解析该tlp包并完成相关处理后,将需要返回Host的tlp包存入另一块内存空间并通知FPGA,FPGA读回该tlp包;

(5)FPGA对FPGA将SoC侧读回的包进行分流;

(6)FPGA将SoC侧读回的包进行信用查询管理;

(7)FPGA根据信用查询结果转为CPL或者CPLD包返回给Host侧。

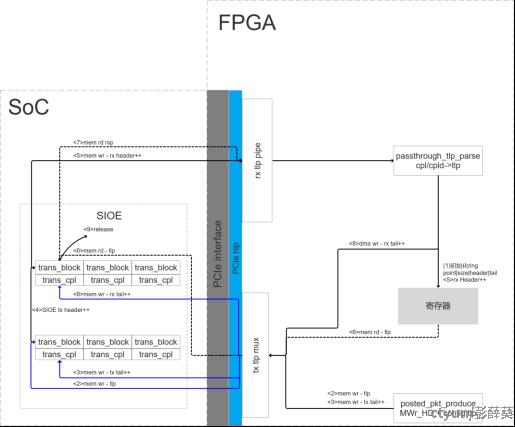

FPGA透传通道和SoC依托ring机制实现FPGA和SoC之间的数据交互。对于单个控制通道,由rx 方向的trans block ring和trans cpl ring、tx方向的trans block ring和trans cpl ring组成。其中,tx trans block用于存储FPGA传送的Host侧完整的tlp包,tx trans cpl用于FPGA写入当前已写tx trans block的指针tail和tlp包长度信息,而rx trans block用于存储SoC处理后需要回传给Host的tlp包,rx trans cpl用于FPGA写入当前已读取rx trans block的指针tail和tlp包长度信息。FPGA寄存器内部维护SoC的指针header和FPGA的指针tail,其中SoC侧的指针header由SoC通过写入寄存器方式更新。具体流程如下:

(1)SoC和FPGA启动后,SoC进行初始化流程,申请4块连续内存空间用于trans block ring和trans cpl ring,并将ring的pointer、size、header、tail等信息写入FPGA寄存器,完成后,FPGA的SIOE rdy信号拉高,代表透传通道可用;

(2)当透传通道工作时,FPGA将封装了config tlp作为payload的Memory write包写入SoC tx trans block;

(3)FPGA更新FPGA tx tail,并将FPGA tx tail和(2)写入的包length写入SoC tx trans cpl;

(4)SoC检测到tx trans cpl的更新,读取tx trans block中的tlp包并进行解析处理,处理完成后将需要回传Host的tlp包写入rx trans block;

(5)SoC更新SoC tx header和SoC rx header,并将SoC rx header写入FPGA寄存器;

(6)FPGA检测到SoC rx header的更新,会对SoC发起一次Memory Read读rx trans block操作;

(7)FPGA接收SoC返回的rx trans block的tlp包并处理;

(8)FPGA更新FPGA rx tail,并将FPGA rx tail写入SoC rx trans cpl;

(9)SoC检测到rx trans cpl的更新,释放对应的rx trans block。

图二 FPGA透传通道和SoC交互流程