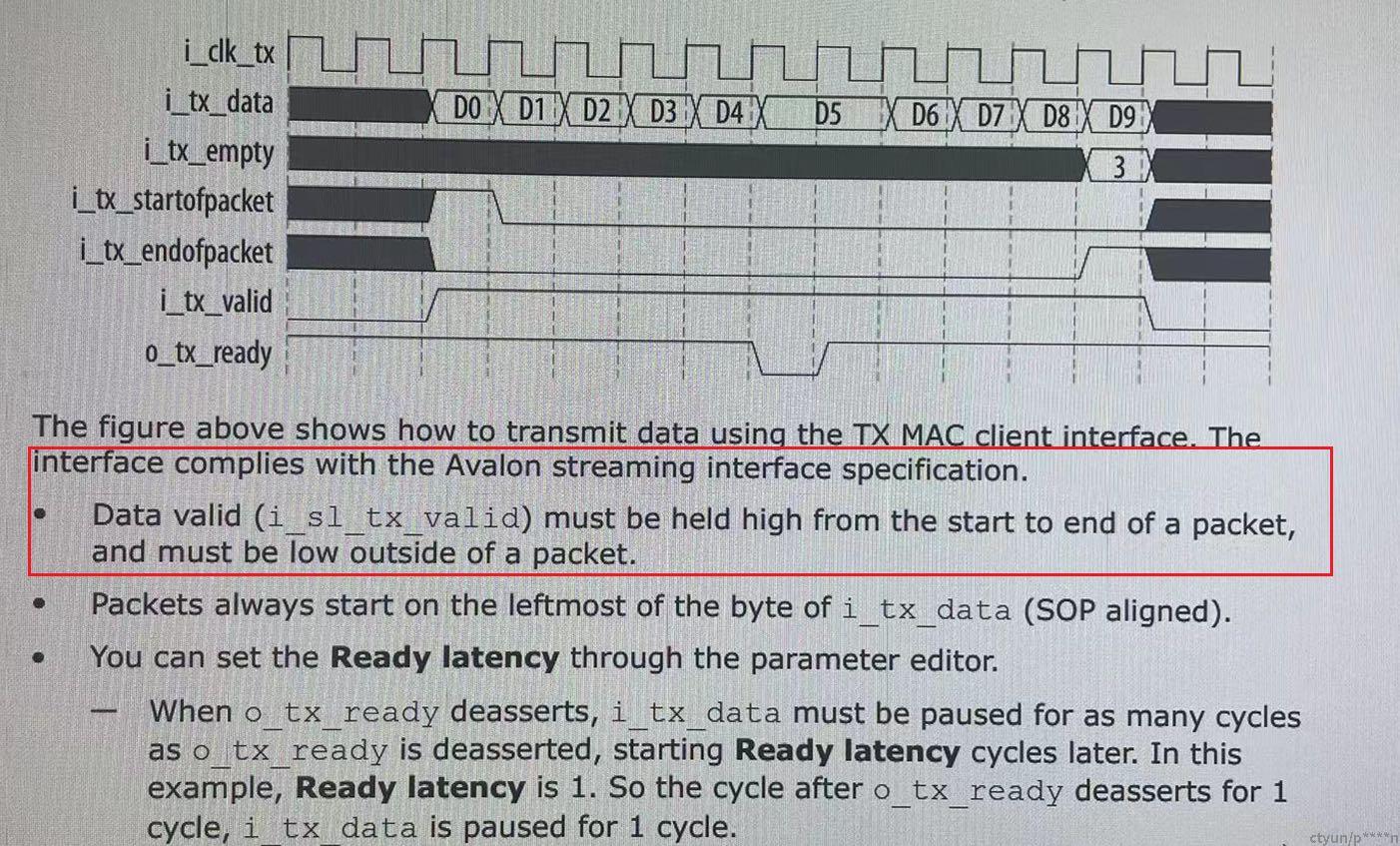

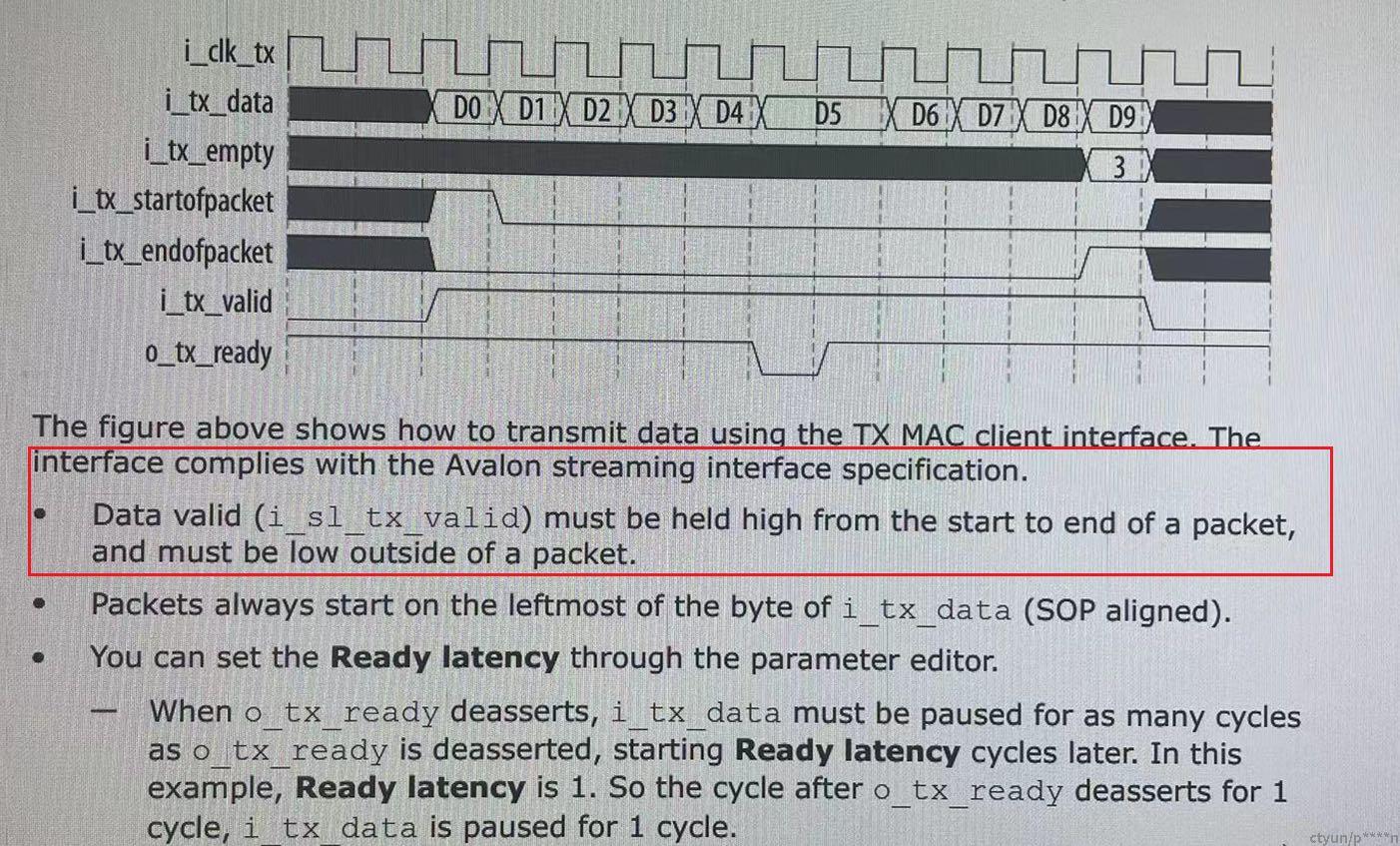

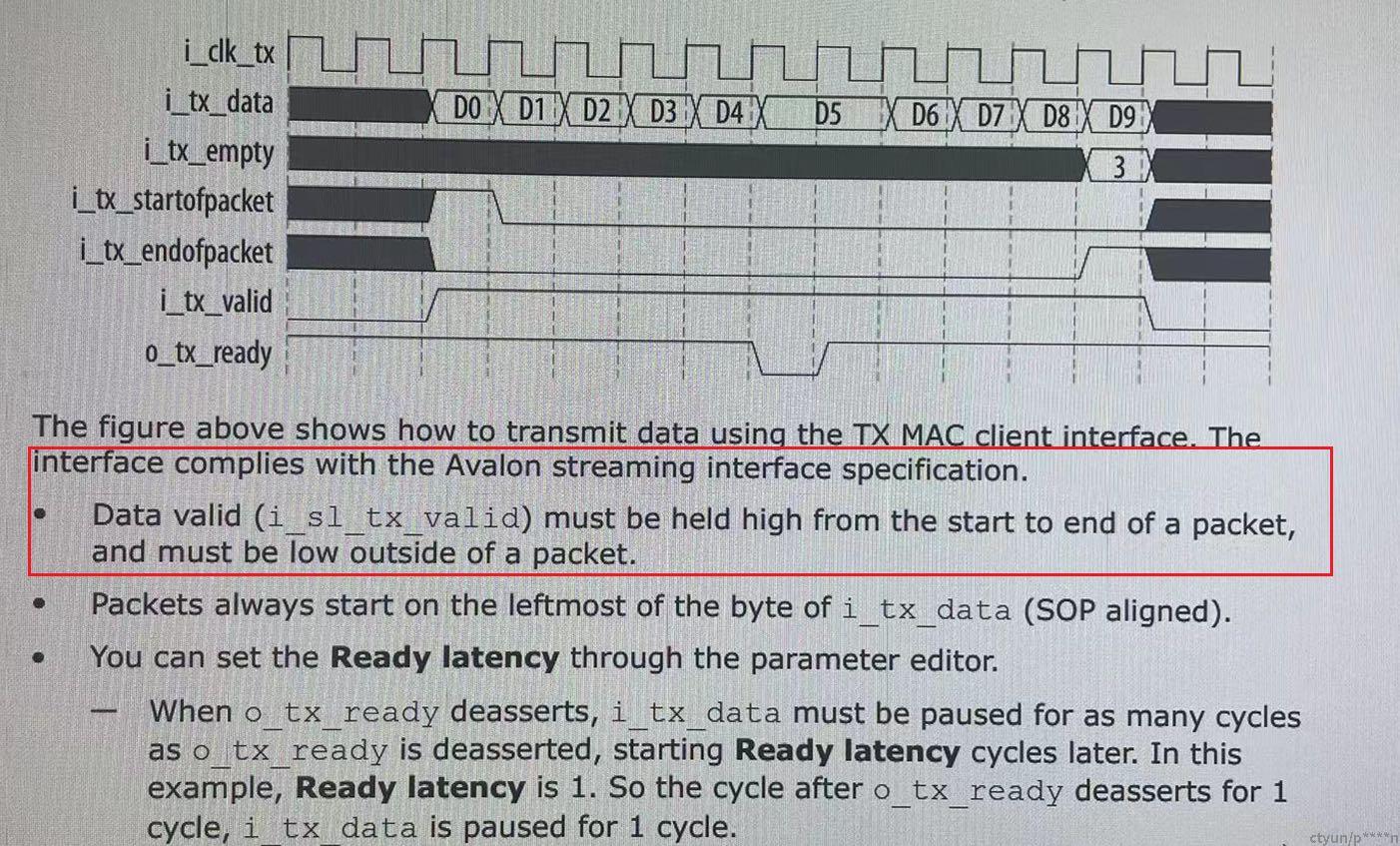

在FPGA设计中,有时要使用到mac ip,像Intel的某些mac ip,对tx方向有整包连续接收的要求,即valid在sop和eop之间必须拉高,这就对相关的fpga设计提出了整包发送的要求。

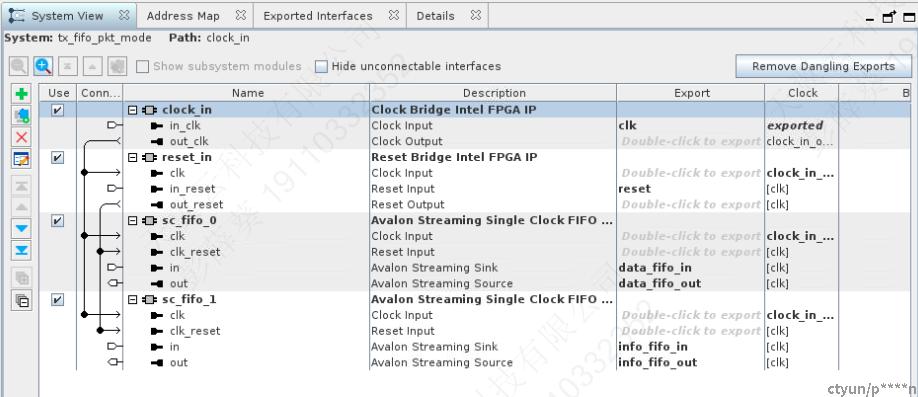

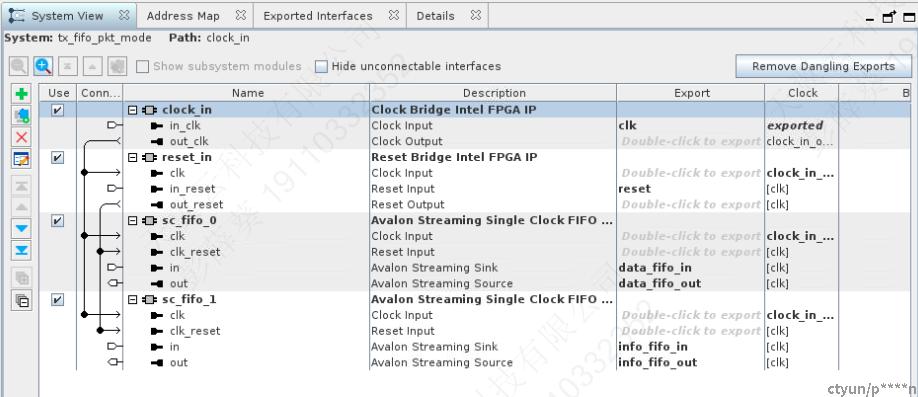

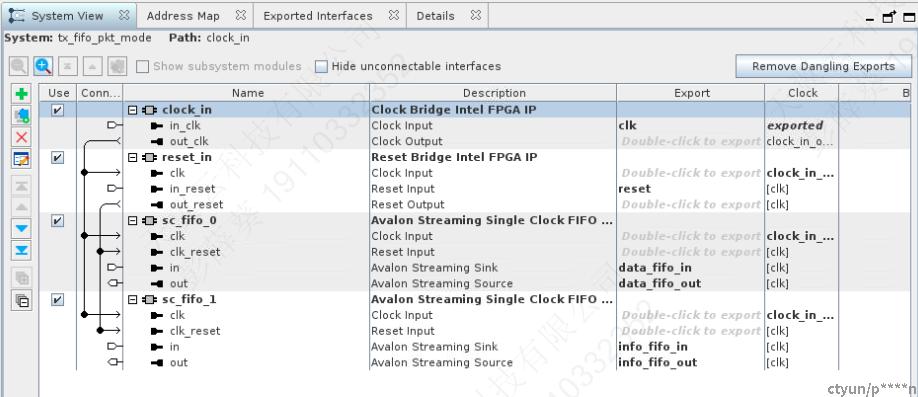

本文使用两个Avalon Streaming Single Clock FIFO搭建platform design用于整包发送,一个用来缓存网络包data,一个用来缓存网络包info。

本文使用两个Avalon Streaming Single Clock FIFO搭建platform design用于整包发送,一个用来缓存网络包data,一个用来缓存网络包info。

在逻辑实现上,info FIFO由网络包为单位进行更新,同时触发data FIFO以整包模式输出。

在FPGA设计中,有时要使用到mac ip,像Intel的某些mac ip,对tx方向有整包连续接收的要求,即valid在sop和eop之间必须拉高,这就对相关的fpga设计提出了整包发送的要求。

本文使用两个Avalon Streaming Single Clock FIFO搭建platform design用于整包发送,一个用来缓存网络包data,一个用来缓存网络包info。

本文使用两个Avalon Streaming Single Clock FIFO搭建platform design用于整包发送,一个用来缓存网络包data,一个用来缓存网络包info。

在逻辑实现上,info FIFO由网络包为单位进行更新,同时触发data FIFO以整包模式输出。

版权声明:本文内容系天翼云实名用户自发贡献,版权归原作者所有,天翼云开发者社区不拥有其著作权,亦不承担相应法律责任,未经许可,不得转载。

如有疑问或争议,请联系ctyunbbs@chinatelecom.cn删除。

在FPGA设计中,有时要使用到mac ip,像Intel的某些mac ip,对tx方向有整包连续接收的要求,即valid在sop和eop之间必须拉高,这就对相关的fpga设计提出了整包发送的要求。

本文使用两个Avalon Streaming Single Clock FIFO搭建platform design用于整包发送,一个用来缓存网络包data,一个用来缓存网络包info。

本文使用两个Avalon Streaming Single Clock FIFO搭建platform design用于整包发送,一个用来缓存网络包data,一个用来缓存网络包info。

在逻辑实现上,info FIFO由网络包为单位进行更新,同时触发data FIFO以整包模式输出。

版权声明:本文内容系天翼云实名用户自发贡献,版权归原作者所有,天翼云开发者社区不拥有其著作权,亦不承担相应法律责任,未经许可,不得转载。

如有疑问或争议,请联系ctyunbbs@chinatelecom.cn删除。