| Chiplet是什么?

Chiplet是一种全新的芯片设计理念。为了便于理解,咱们先来看看目前的芯片是怎么设计出来的。

大家会经常听到SoC这样一个芯片代名词。它是把很多的功能模块,比如CPU、存储器、接口这些通通集成在一个芯片上,做成一个大芯片。

而Chiplet呢,与SoC反其道而行之,字面上翻译叫做“芯粒”,可以理解为小芯片的意思。

在Chiplet设计理念下,是将原本SoC中的每个功能模块都单独拆出来,做成具有单独功能的一个个小芯片单元。

之后,通过先进封装技术,像搭积木一样,把这些小芯片再集成为一个系统级芯片。

| Chiplet、 SoC、SiP的区别

SoC(system on chip)叫做片上系统。是围绕CPU,将各种功能模块都集成在一颗芯片上的产物。

而Chiplet则不同,是先将各个功能模块做成小芯片,之后再封装到一起,组成系统级芯片。

表面上看,似乎只是制造工序的区别,其实Chiplet与SoC本质的不同是“异构异质”。异构集成,指的是可以将不同工艺的芯片集成到一起。

在SoC中,由于是在一个芯片中进行集成的,所以各个功能模块必须采用同一工艺制程,要是14nm的都是14nm的,要是7nm的都得是7nm的。

而在Chiplet模式下,不同工艺的芯片可以凑到一起。比如CPU用7nm的,接口芯片用14nm的。这就是异构的概念。

异质集成,是指不同材料的芯片可以集成为一体。SoC肯定是办不到的。而Chiplet模式下,可以将Si、GaN、InP等等不同材质的小芯片集成到一起。

SiP(system in package)指系统级封装。通过将多种功能的芯片,包括处理器、存储器、FPGA等功能芯片集成在一个封装内,从而实现一个完整的系统。

在概念上来讲,SiP与Chiplet很像。并且SiP同样能够实现异构异质集成的。而它们两者的区别在于,SiP是将不同芯片封装在一个基板上,Chiplet则是封装到芯片上。

因此,Chiplet还是属于芯片,而SiP只能算作小系统。Chiplet能达到SoC的性能

而SiP则不一样,因此Chiplet多用于高性能领域,SiP多用于小型化消费级产品。

| Chiplet的价值

可能有人会说,相比SoC,Chiplet工序既繁琐、又无法完全超越SoC的性能。但Chiplet确实存在它的意义:

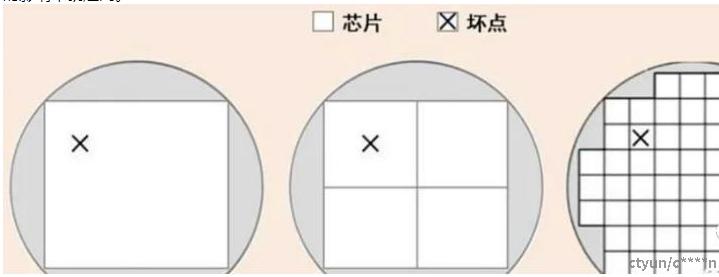

芯片的良品率与芯片面积有关,芯粒技术设计将大芯片分成小模块可以有效改善良品率,降低因不良率导致的成本增加。

在芯片制造过程中,一片晶圆有固定的缺陷率。遇到这些无法修复的坏点,只能把它剔除掉。在同样缺陷分布的情况,切割裸片的的尺寸越大,缺陷的影响率就越高。

单颗SoC芯片的尺寸会随着集成规模的扩大而越来越大。当一颗芯片的尺寸达到400甚至600平方毫米时,芯片的良率就会变得很低。这时采用Chiplet模式,将大芯片拆成一个个小芯片,其芯片的良率将会提高。

芯粒技术通过在芯片设计阶段就将Soc(系统级晶片)按照不同功能模块分解成可重复运用的小芯粒,是一种新形式的IP复用,可大幅度降低设计复杂度和成本累次增加。

在系统级芯片上,很多功能模块都是标准化的。那么在Chiplet模式下,应用厂商就可以生产出很多标准化的芯粒,下游客户直接购买芯粒进行封装就可以了。

这就相当于芯粒的重复使用,无形中降低了开发难度,提升了效率。

此外,Chiplet模式具有异构集成的特点。有时候一颗高性能芯片,只需要CPU满足更高制程,其他芯片制程低一些没关系。

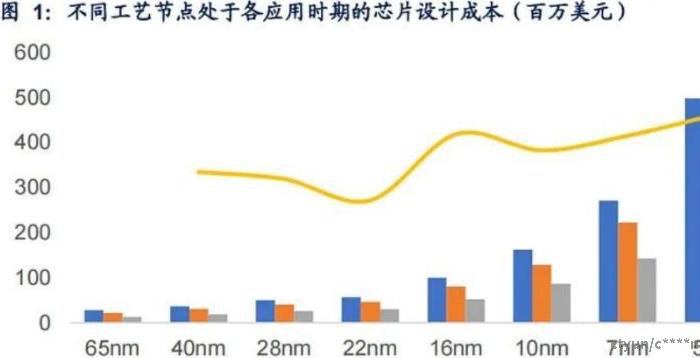

在SoC中,所有功能模块都得跟着最高制程走。而在Chiplet模式下就可以区别配置。由于SoC上所有功能模块需同步迭代,伴随制程提高,芯片设计成本随之大幅增长。在工艺节点为 28nm 时,单颗芯片设计成本约为 0.41 亿美元,而工艺节点为 7nm 时,设计成本快速提升至 2.22 亿美元。

Chiplet模式下,芯粒可以选择性迭代,这种复用的结果会明显节约设计成本、缩短研发周期。

-

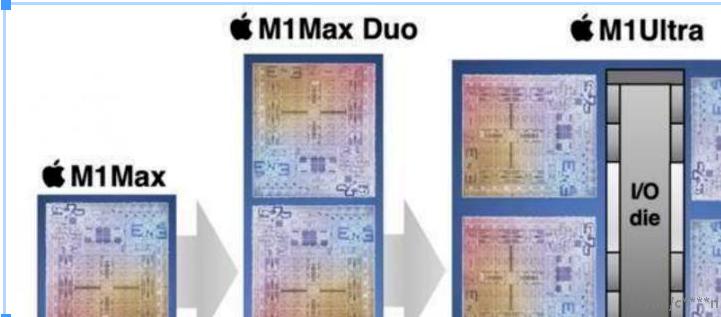

一是按照功能将不同模块拆分,比如AMD的三代锐龙处理器。

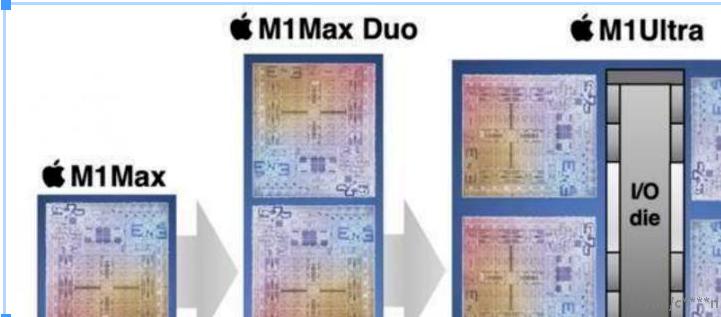

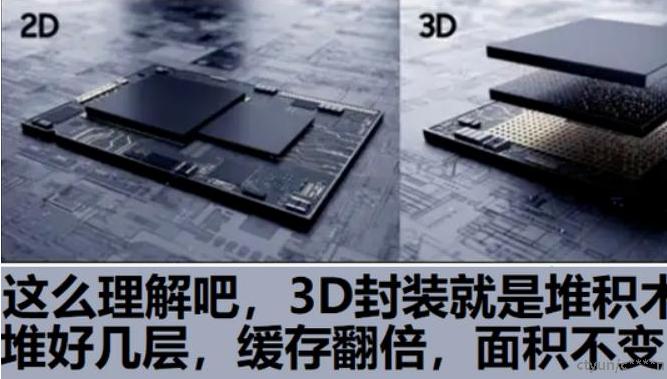

二是把具备完整功能的小芯片集合起来(俗称“芯片堆叠"),目的是实现性能的增长。比如苹果的M1 Ultra芯片,就是堆叠了两颗M1 Max芯片,从而获得两倍算力。

理论上可以通过Chiplet的堆叠,让低端产品实现高端产品的性能。

目前A国对中国高端制程芯片的封锁很严密,于是大家就考虑采用Chiplet技术,拿14nm、28nm的芯片堆叠出7nm、5nm的理想化的效果,实际上是做不到的,只能得到“1+1<2”结果。

Chiplet只能说是一种芯片的设计理念,真的要把一个个芯粒拼装在一起,关键得看封装技术能不能跟得上。

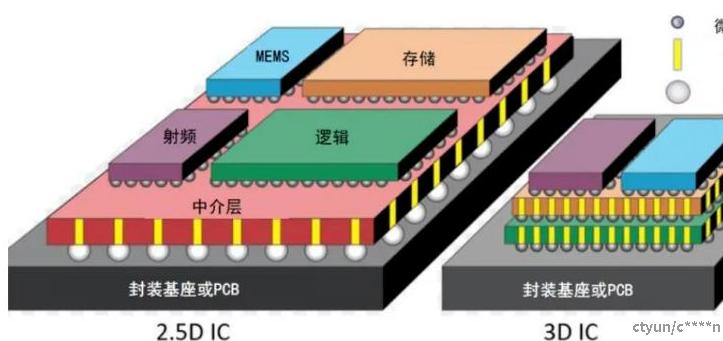

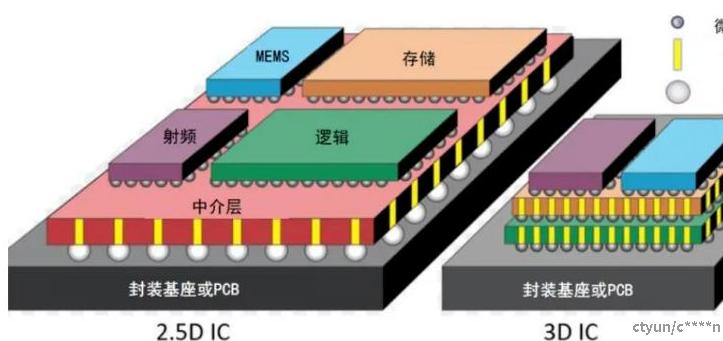

2.5D和3D先进封装,是配合Chiplet的工艺手段。

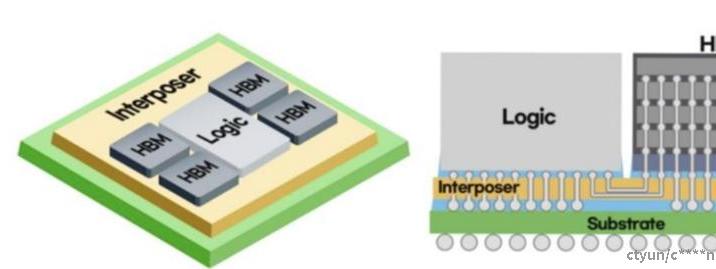

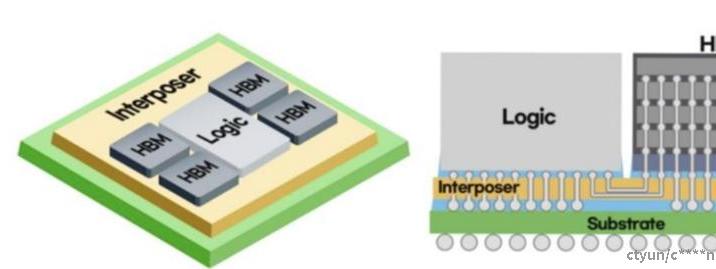

2.5D封装,是目前应用于Chiplet模式的主流方案,整体技术相对比较成熟。

什么是2.5D封装?说白了就是把一个个芯粒并列排布封装在一起。

不同芯粒之间如何实现互联互通,需要在下层PCB板与上层芯粒间,加入一片硅中介板(Silicon Interposer)。

硅中介板本身没什么特别的,类似于一颗没有功能的晶圆。但难点在于,要在Interposer内部做很多硅通孔(TSV),起到电气垂直互联的作用。

这个工艺难度还是不小的。目前2.5D封装代表技术有三种,分别是台积电的CoWoS、英特尔的EMIB以及三星的I-Cube。

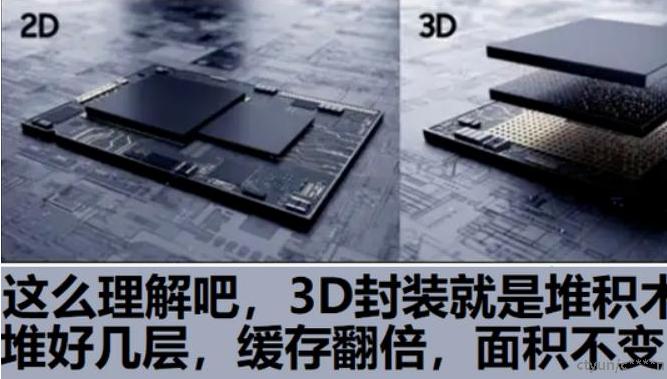

3D封装相比2.5D能够实现更高密度的堆叠。相比2.5D,小芯片可以直接摞在一起,这就需要在小芯片内直接制作硅通孔(TSV)。因此难度更大。

目前3D封装技术还不是很成熟。比较完善的是应用在DRAM领域,可以实现100多层的上下堆叠,但这都是同质范畴的,异质堆叠还没那么快。

3D封装技术目前主要有台积电的SoIC、英特尔的Foveros、三星的X-Cube。它们有晶圆制造能力,利用卡位优势,开发自己的先进封装技术。

当然传统封测厂同样也没闲着,在2.5D/3D封装技术上都有布局。比如国内通富微电、长电科技等等。

因此,Chiplet理想很丰满,但需要依托封装技术才能实现。

随着摩尔定律走到极限,芯粒技术被行业普遍认为是未来5年算力的主要提升技术。

华为、AMD、英特尔等行业巨头都积极布局芯粒并推出相关产品,2022年3月英特尔等多家巨头联合推出通用芯粒互联标准UCle;12月,首个中国小芯片标准发布。

对中国而言,产业中短期内无法破解EUV光刻机卡脖子瓶颈,实现7nm以下工艺难度大,因此芯粒技术或将被寄予厚望,成为我国突破半导体工艺被卡脖子的重要途径。

芯粒技术是先进制造工艺的补充,而不是颠覆式的替代。

芯粒领域有很多技术挑战,还要满足不同应用场景的不同技术诉求,不会只停留在成熟工艺区间。

这意味着我国科研人员依然要攻坚克难,加快多学科协同的技术攻关。