1. 什么是 HPS(硬核处理器系统)

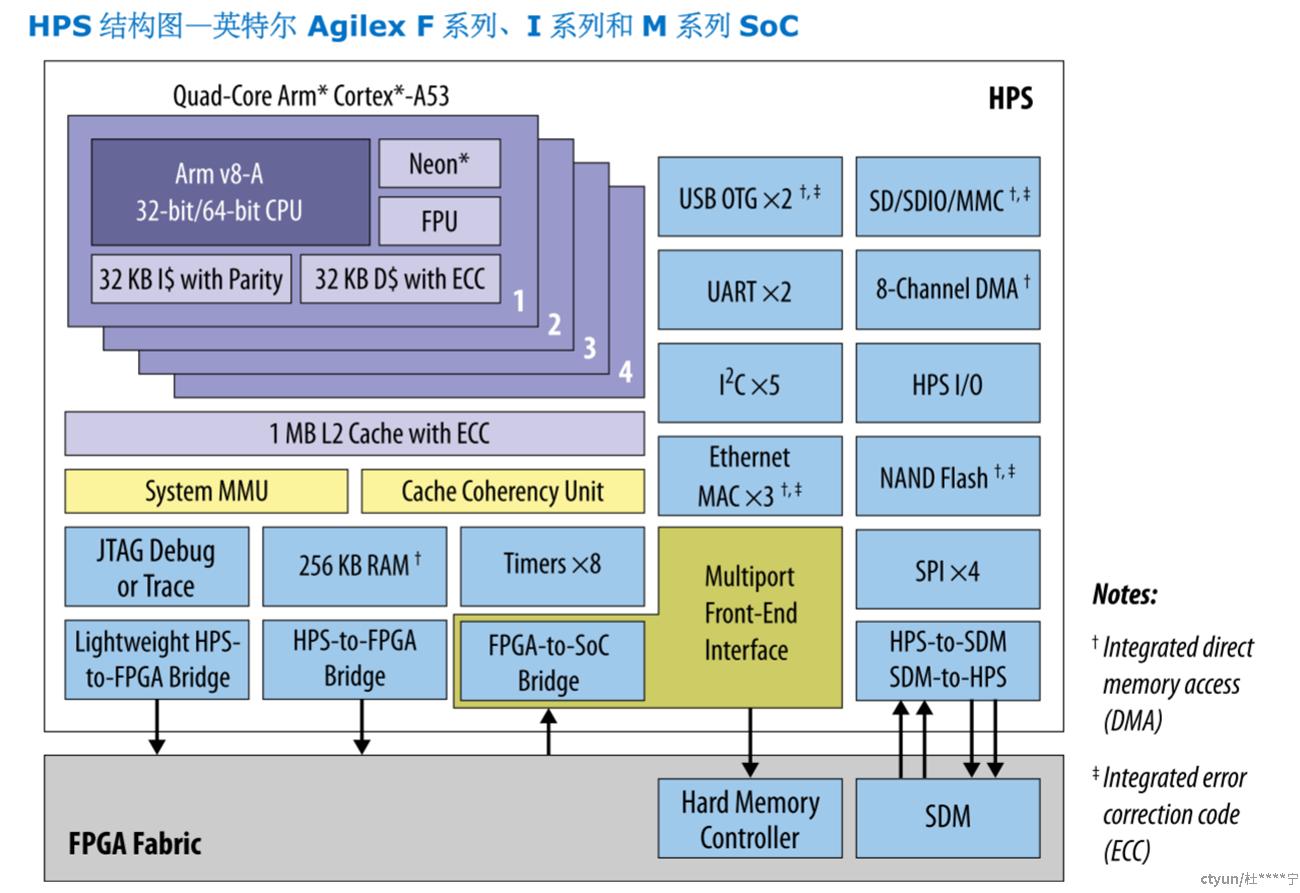

HPS(Hard Processor System,硬核处理器系统)是集成在SoC FPGA中的一组高性能处理器和外设模块。作为硬核,HPS 相比于软核处理器(如 Nios II)具有更高的运行效率和更强的性能。HPS 的概念主要源自 Intel(原 Altera)的 SoC FPGA 产品,例如 Intel Cyclone V 和 Intel Arria 10 系列。这些 SoC FPGA 将高性能的 Arm Cortex-A 系列处理器与 FPGA 逻辑资源集成在同一芯片上,形成了一种独特的异构计算架构。

在 Intel SoC FPGA 中,HPS 通常基于 Arm Cortex-A9 或 Cortex-A53 多核处理器,具备内存控制器、丰富的外设接口(如 UART、SPI、I2C、USB 等)以及高效的 AXI 总线架构。HPS 的设计目标是提供强大的通用计算能力,同时与 FPGA 部分紧密协作,实现灵活且高性能的嵌入式系统解决方案。

通过将 HPS 与 FPGA 结合,开发者可以在同一芯片上同时运行复杂的软件任务(如操作系统、协议栈)和硬件加速任务(如信号处理、数据包转发),从而显著提升系统的整体性能和能效。这种架构特别适用于工业自动化、网络通信、嵌入式视觉等需要高性能计算和实时处理的领域。

1.1 HPS 的核心组成——以 Intel Agilex 系列 SoC 为例

- 微处理单元(MPU)

- 基于Arm Cortex-A系列(A9、A53等)内核。

- 双核或四核架构,支持多任务操作。

- 内存接口

- 支持DDR3、DDR4等内存,提供高宽带访问能力。

- 内置多端口内存控制器(MPFE),实现多主设备访问调度。

- 外设接口

- 提供丰富的外设,包括UART、SPI、I2C、EMAC、USB、SDMMC等。

- 与主流嵌入式系统外设兼容,方便软件开发。

- 总线结构

- 采用标准的AXI总线架构,与FPGA部分通过多个桥接接口进行通信。

1.2 HPS的运行模式

HPS既可以单独运行嵌入式操作系统(如Linux、FreeRTOS等),也可以通过总线与FPGA逻辑部分协作,完成复杂的嵌入式系统设计。

2. HPS在SoC FPGA中的作用

HPS是SoC FPGA中不可或缺的核心组件,提供了计算能力、外设管理和操作系统支持,极大地拉展了FPGA的应用范围。

2.1 HPS与FPGA的协作机制

- HPS作为主控单元 HPS运行嵌入式操作系统,承担系统的主控任务,如网络管理、用户控制界面处理等。FPGA部分则负责高性能数据处理任务,如信号处理和数据加速。

- 数据交互与任务分工

- HPS-FPGA桥接接口:通过AXI总线实现HPS与FPGA之间的数据传输和指令交互。

- 中断机制:HPS可通过中断机制与FPGA实时通信,即时响应外部事件。

2.2 HPS的应用场景

- 工业自动化 HPS运行实时操作系统,管理工业通信协议标准栈,FPGA处理高速I/O信号与复杂逻辑。

- 网络加速 HPS处理网络协议标准栈,FPGA加速数据包转发与过滤。

- 嵌入式视觉系统 HPS运行嵌入式Linux,管理摄像头接口与显示屏,FPGA进行实时视频处理与加速。

3. 基于 HPS 的开发流程

开发基于 HPS 的嵌入式系统需兼顾硬件与软件两大方向。Intel 提供了 Golden System Reference Design (GSRD) 参考设计以简化开发,但其依赖官方开发板,难以适配自定义硬件。因此,本系列文章将详细讲解以下两种硬件开发方法:

3.1 硬件开发方法对比

- 基于 GSRD 的快速开发

- 优点:

- 开箱即用:提供预配置的 HPS 外设接口、FPGA 逻辑和完整软件栈(Linux 镜像),大幅缩短开发周期。

- 验证可靠:官方测试用例和硬件兼容性保障,降低调试风险。

- 缺点:

- 灵活性受限:仅适配 Intel 官方开发板,自定义硬件需反向修改设计,可能引入兼容性问题。

- 依赖过时工具:GSRD 基于旧版 Quartus 和 SoC EDS,新型号芯片(如 Agilex)支持有限。

- 完全自定义开发

- 优点:

- 高度灵活:可自由配置 HPS 参数(内存控制器、外设接口等),适配任意自定义板卡。

- 资源优化:按需设计 FPGA 逻辑,最大化利用芯片资源(如专用硬核)。

- 缺点:

- 开发周期长:需手动配置 HPS 与 FPGA 桥接、时序约束,调试复杂度高。

- 硬件验证挑战:需单独验证电源、时钟、信号完整性,对开发者经验要求较高。

3.2 软件开发流程

无论采用哪种硬件方法,软件开发均需以下步骤,但工具链需适配芯片型号:

- 操作系统构建:

- GSRD 方法:直接使用预编译的 Linux 镜像(基于 Yocto),仅需简单设备树修改。

- 自定义方法:需从源码编译 Linux 内核(推荐使用 ARM Development Studio 或 Buildroot),并手动编写设备树描述硬件拓扑。

- 驱动开发:

- 为 HPS 外设(如 Ethernet、USB)和 FPGA 逻辑接口开发 Linux 驱动,自定义方法需额外处理 FPGA 端寄存器映射与中断协调。

- 应用程序开发:

- 基于 C/C++ 或 Python 实现业务逻辑,通过驱动接口操作 HPS 外设与 FPGA 加速模块。

工具链注意事项:

- SoC EDS 的替代方案:Intel 已停止更新 SoC EDS,新型号芯片建议使用 ARM DS 或开源工具链(如 GCC + OpenOCD)。

- 调试支持:结合 JTAG 调试 HPS 启动流程,利用 System Console 或 Signal Tap 分析 FPGA 逻辑交互。

3.3 本系列文章的目标

- 介绍GSRD 开发方法:通过官方参考设计快速上手 HPS 基础功能,适合初学者或原型验证。

- 介绍自定义HPS系统开发方法:从零构建 HPS 系统,深入解析硬件配置、软件移植与调试技巧,满足工业级定制需求。

通过对比两种方法的优缺点,开发者可依据项目需求选择路径,后续章节将逐步展开实践细节。

intel官方GSRD:GSRD 用户指南 - Altera FPGA 开发人员

4. HPS开发工具链与生态系统总结

4.1 开发工具

- Quartus Prime:FPGA设计工具。

- Platform Designer:HPS与FPGA系统集成工具。

- SoC EDS:嵌入式软件开发工具套件,包含U-Boot、Linux BSP与示例代码。

- Arm Development Studio:支持HPS侧嵌入式应用程序与驱动开发。

4.2 支持的操作系统

- 开源系统:Yocto Linux、FreeRTOS、uClinux等。

- 商业系统:VxWorks、QNX、ThreadX等。

4.3 第三方IP与设计实例

- Golden System Reference Design :官方提供的硬件与软件参考设计。

- 第三方IP核:支持以太网、PCIe、USB等常见外设的软核IP。