上一篇讲到,在vivado里面对异步路径进行同步时,尽量使用xilinx提供的xpm模块来进行。此时开发者不需要做任何额外的约束(不要对两个异步时钟加set_false_path或者set_Clock_Groups约束),vivado工具本身会自动对异步路径进行约束,本篇文章就做一个实验来说明一下原因。

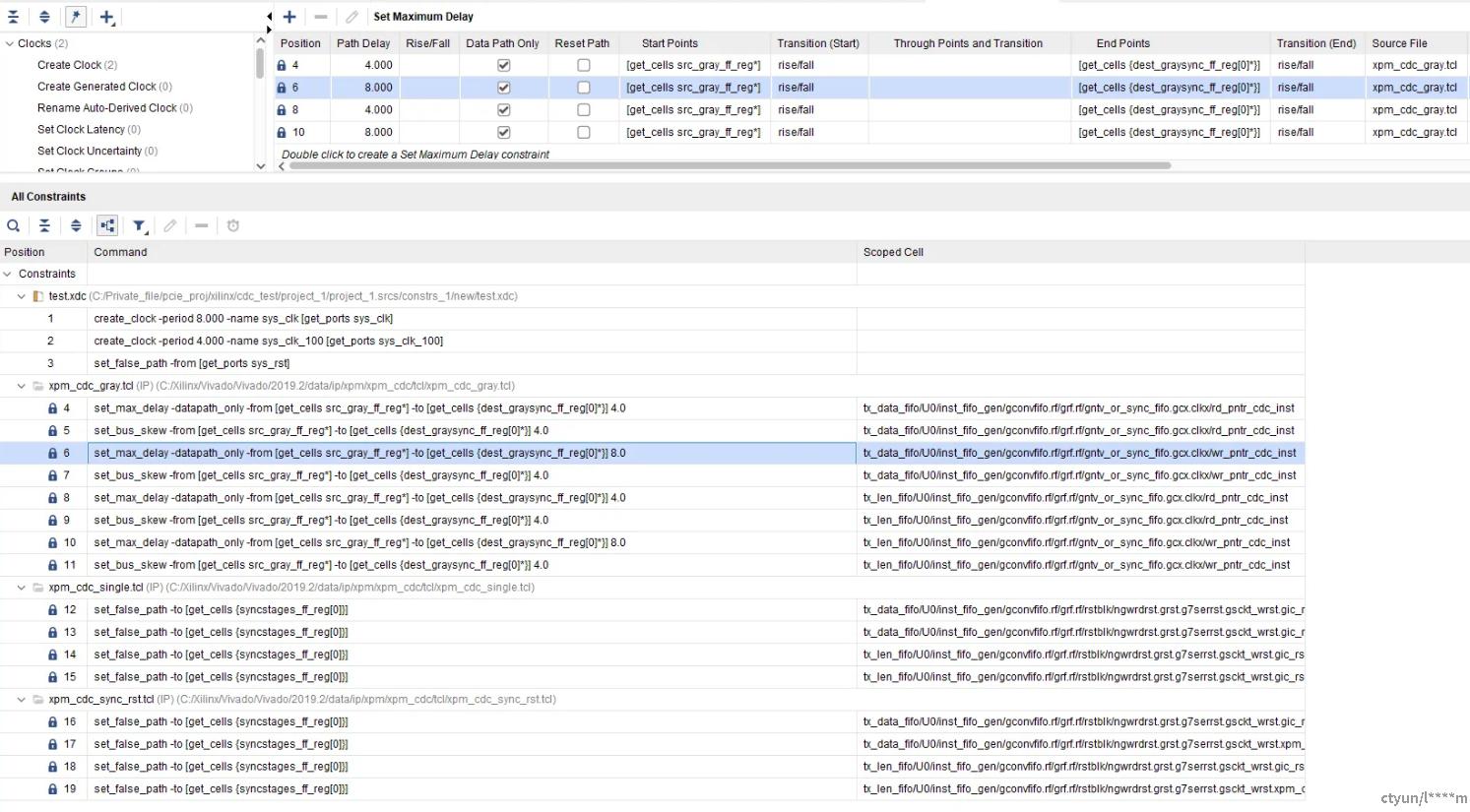

自己建立了一个使用异步FIFO做跨时钟域处理的工程,只约束了以下内容:create_clock -name sys_clk -period 8.000 [get_ports sys_clk] create_clock -name sys_clk_100 -period 4.000 [get_ports sys_clk_100] set_false_path -from [get_ports sys_rst]

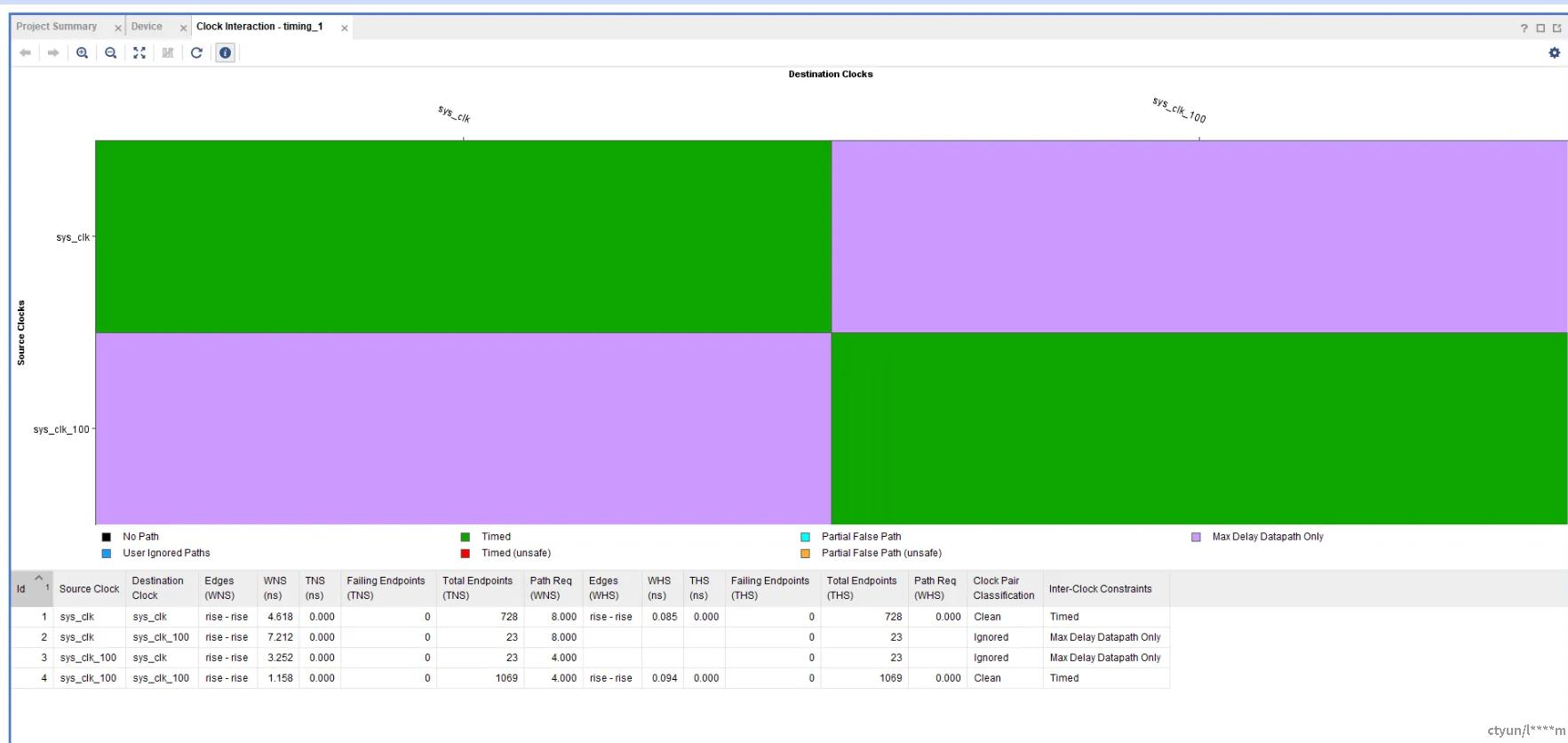

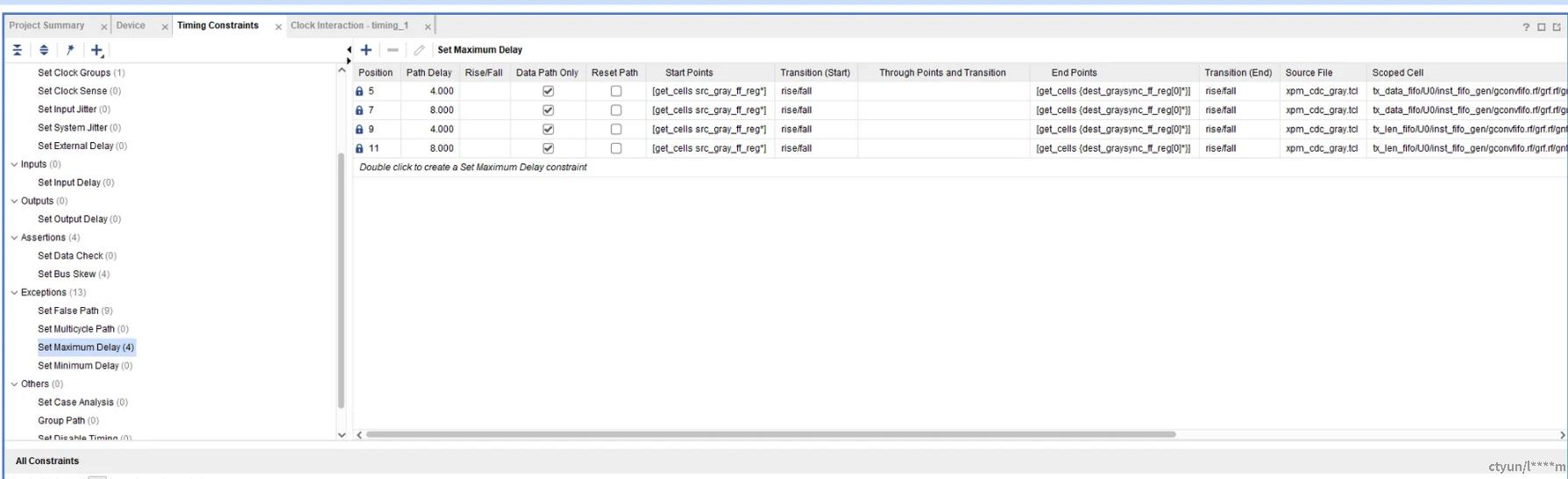

添加异步时钟组约束之前:

图1

图2

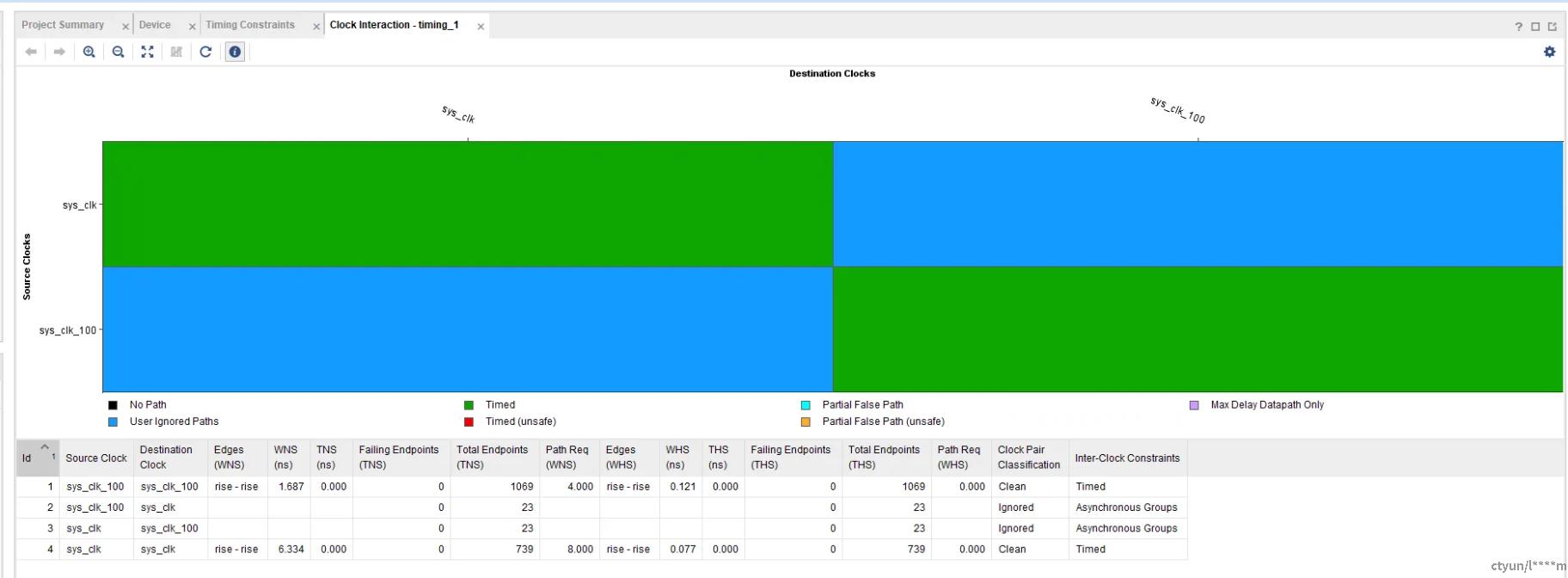

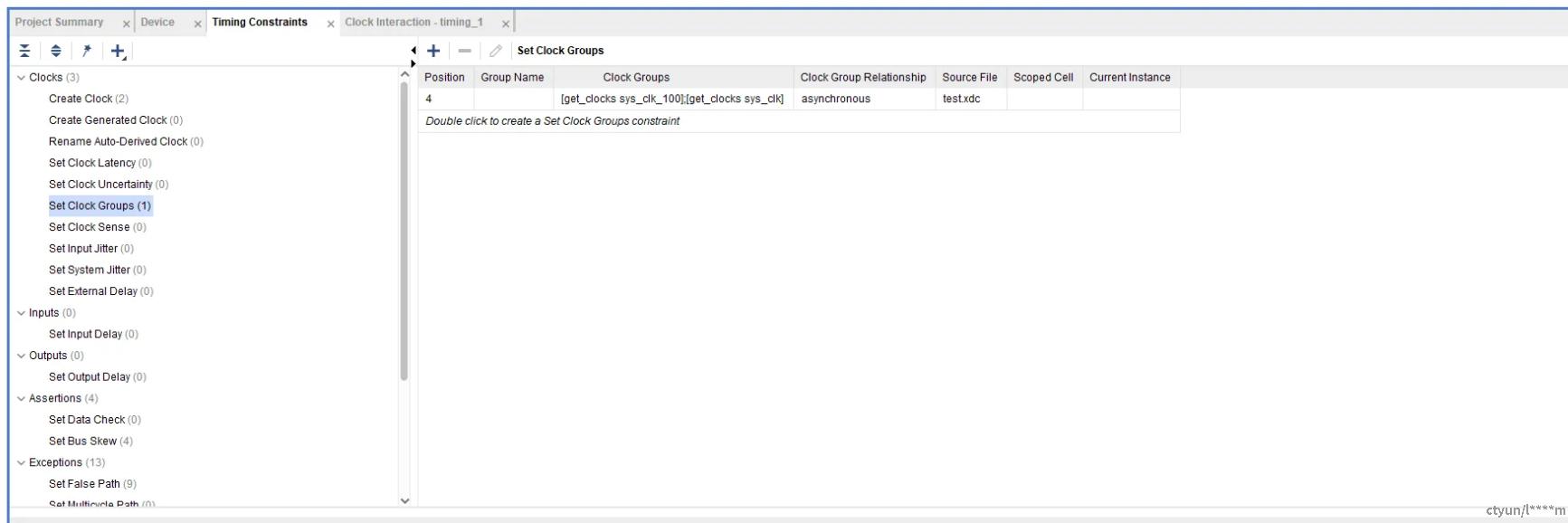

可以看到xilinx内置有自己的最大延时和最小延时约束。而且已经生效。在将两个时钟设置为异步时钟组之后,编译结果如图3所示。

图 3

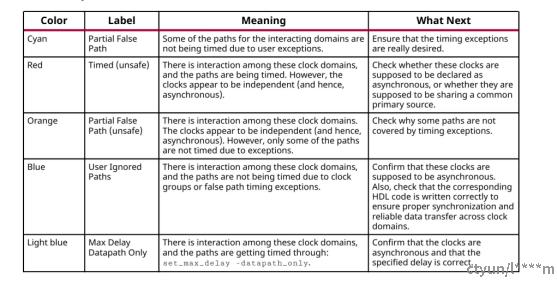

图 4 官方文档说明

Orange

There is interaction among these clock domains.The clocks appear to be independent (and hence, asynchronous). However, only some of the paths are not timed due to exceptions.

这些时钟域之间存在相互作用。时钟看起来是异步的。但是,由于时序例外,只有部分路径不计时。

Check why some paths are not covered by timing exceptions.

需要检查一下为什么一些路径是没有被时序例外的约束覆盖。

blue

这些时钟域之间存在交互,并且由于时钟组或错误的路径定时异常,路径不会被定时。

确认这些时钟应该是异步的。此外,检查相应的HDL代码是否正确编写,以确保正确的同步和跨时钟域的可靠数据传输。

light blue

There is interaction among these clock domains, and the paths are getting timed through: set_max_delay -datapath_only.

这些时钟域存在相互作用,路径通过他们进行定时

图 5

图 6

通过上面的图片可以发现增加了时钟组的约束之后,xilinx最大延时和最小延时约束并没有生效。这样就会导致,本来需要去进行时序分析的路径,反而被忽略了。在布局布线时,就会出现一些不易察觉的问题。

总结:

这说明了,对于异步fifo,vivado会自动进行时序例外的约束。所以我们在使用过程中,有使用异步FIFO同步的地方,尽量不要设置异步时钟组。另外,如果不会使用时序例外约束,尽量使用xpm进行数据的同步。Xilinx的xpm同步模块也会有相应的TCL文件自动添加相关的时序例外约束。