二、virtio_blk卸载到FPGA

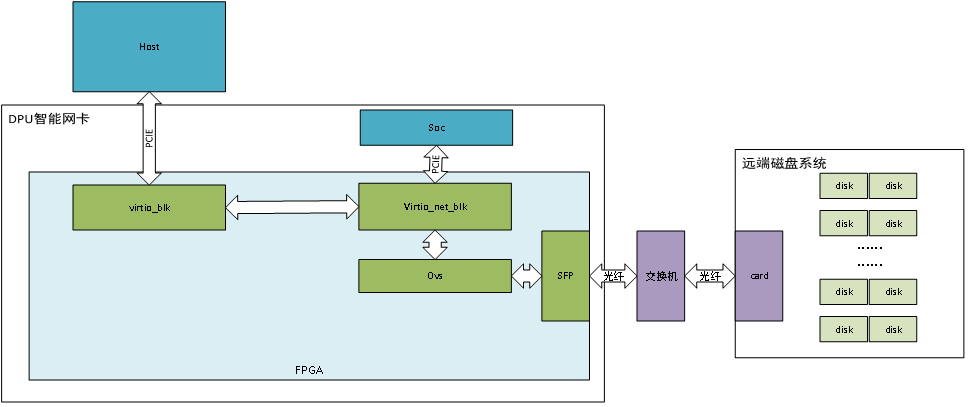

如下图1所示,将virtio_blk卸载到DPU智能网卡中。在智能网卡中,virtio_blk控制器通过PCIE控制器等与host相连接的。host发起的读或者写操作指令,通过virtio_blk的转发,在FPGA处理后,经过virit_net_blk模块送到FPGA外部的SOC上,这里SOC主要是做存储包的拆解、合并、维序和转发等,然后采用TCP协议,由virit_net_blk模块转发到光口上,用光纤与远端的交换机和磁盘进行连接,进而进行块存储设备的读写等操作。

图 1 智能网卡中实现存储数据传输模块结构示意图

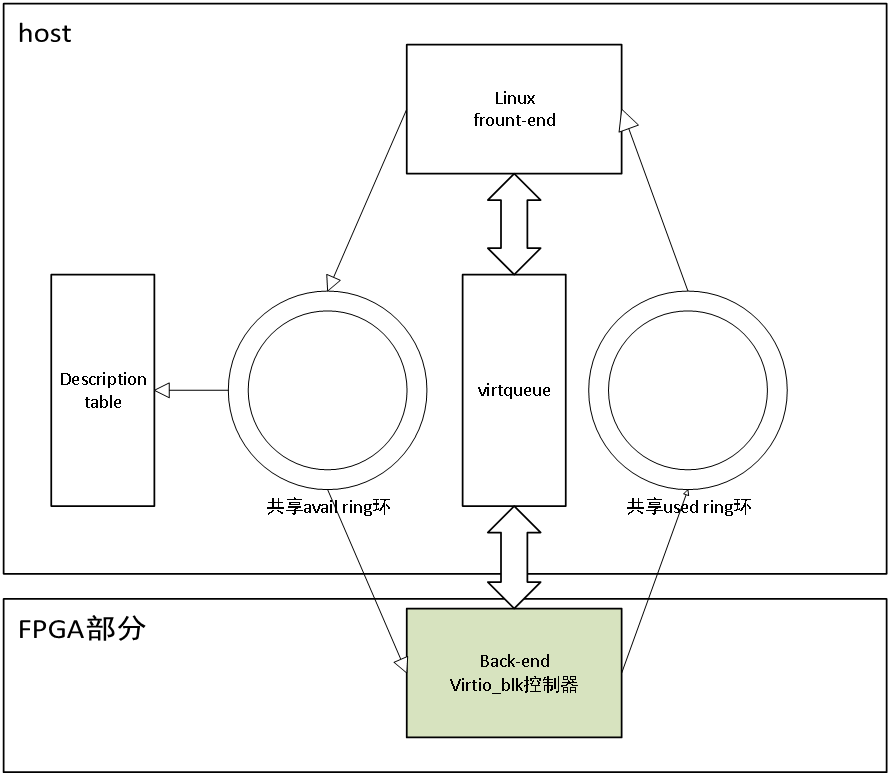

这里简单介绍一下virtio_blk前后端交互过程。如下图2所示,当客户机host需要发送读写IO指令等数据包时,会把数据包构造成逻辑buffer,然后填充到virtqueue,并通过notify机制通知back-end后端。当后端收到通知后,如果当前没有处理其他数据包就开始处理这个队列的请求,否则等待空闲。空闲后,后端从此队列的共享avail_ring中取出buffer head index,以此为地址找到描述符表中对应的描述符位置,然后从对应的描述符中获取到需要发送的数据的起始地址和长度等信息。后端根据这些信息,将数据包从host侧读取出去,转发送到远端的磁盘,进行读写等操作。待到磁盘读写操作完成后,会返回对应的完成信息,后端会将此信息填充到host对应的buffer中,然后更新used_ring。最后采用中断的方式通知host。Host收到中断后,就从used_ring 中获取更新后的 index,以此判断buffer中是否有对应的返回信息,如果有就直接取走,并释放此buffer空间。

图 2 virtio_blk前后端结构示意图