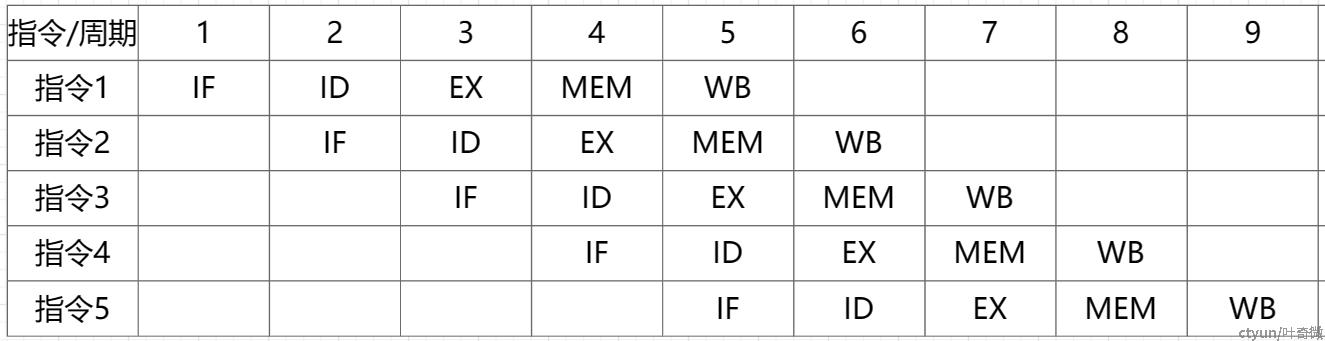

众所周知,cpu中数据的表示和计算是由0和1构成的,加减等计算由众多与、或、非以及其他相关逻辑电路构成,我们将计算用组合电路简略表示为下图y=f(x),x,y可以是一个向量表示单个或多个输入和输出。

由于与或非等门电路组成的组合电路有时延,因此结果y在x输入以后需要一定时间才能够得出。

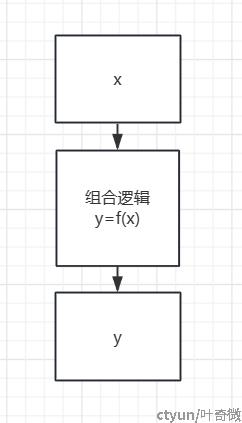

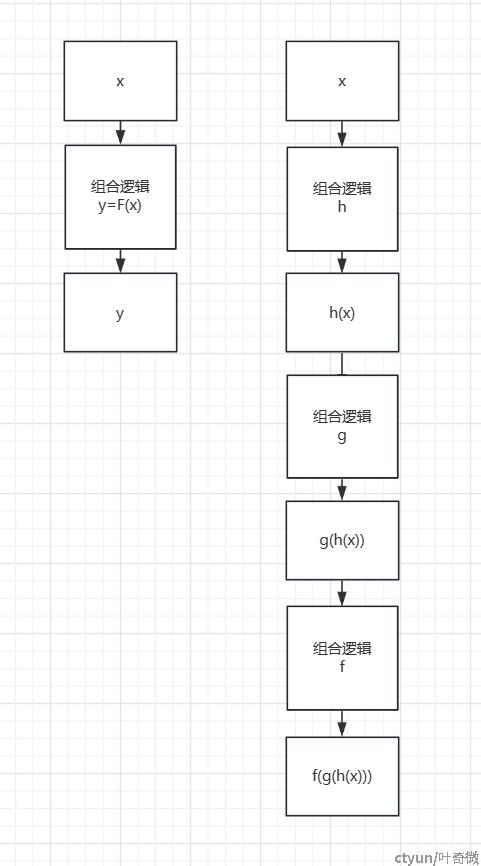

假设有F(x)=f(g(h(x))),假设f,g,h的组合电路时延为50ns,若使用组合电路F(x)完成计算,则需要150ns。

例如假设上图的的两个组合电路同时持续不断计算一个序列x1,x2,x3

左图电路由于需要每次得出y后才能计算下一个x,因此计算完成整个序列需要的时间为150ns*3=450ns

而右图当组合逻辑h计算出h1以后,就可以进行下一个输入x2,组合逻辑g,f同理,因此计算完成整个序列需要的时间为150ns+50ns*2=250ns

可以看出流水线不能使单个计算加快,但是能大幅度提升吞吐能力,使得cpu的运算速度提升。

下图是一个经典的5级流水cpu,可以看出虽然单个指令的执行时间为5个周期,但是之后每个周期都能执行一条指令,执行完成5条指令仅耗时9个周期