现在的制造工艺越来越先进,FPGA内的晶体管数量成几何级增长,在FPGA内实现的工程越来越复杂和庞大使FPGA的综合和实现时间越来越长。FPGA的现场可编程技术适合工程人员快速迭代开发,在开发和定位问题时需要工程人员经常生成FPGA的bit文件,但动辄十几个小时的综合和实现时间,阻碍了开发迭代的进度,其中代码综合占用的时间比例较大。有时候也会遇到在顶层上修改个简单的bug,虽然没有影响到底层文件,但要对整体文件进行综合和实现才能生成FPGA的bit文件,耗时巨大。

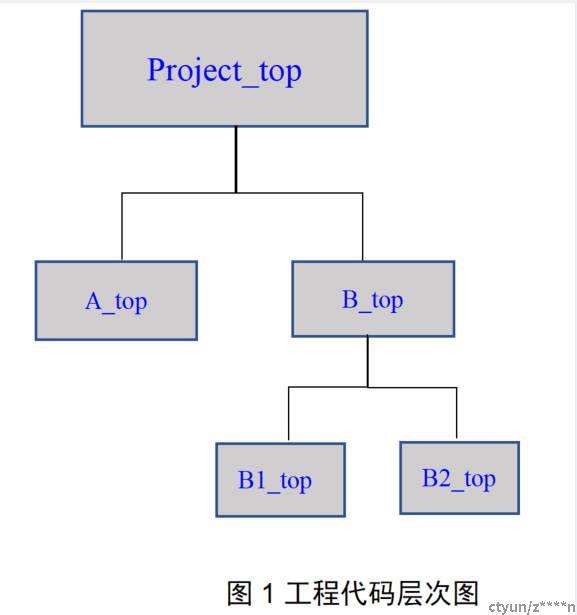

我们可以将工程代码自顶向下分成几个层次,底层代码在上一级中是以空壳形式存在(即只有顶层代码),分层的代码可以分开编译综合。层次结构可以参见图一。如果B_top模块没有修改,A_top模块有修改,则综合时可以直接添加B_top的网表,B_top模块不用再从RTL重新综合。

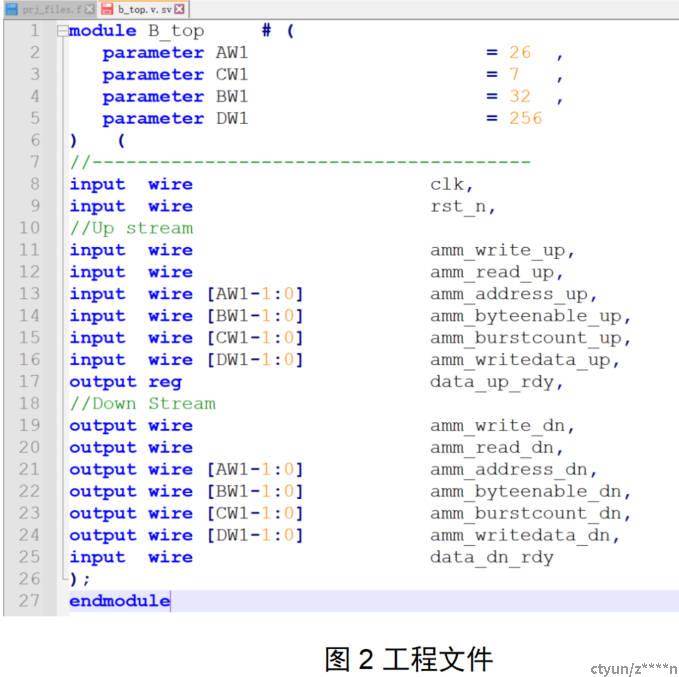

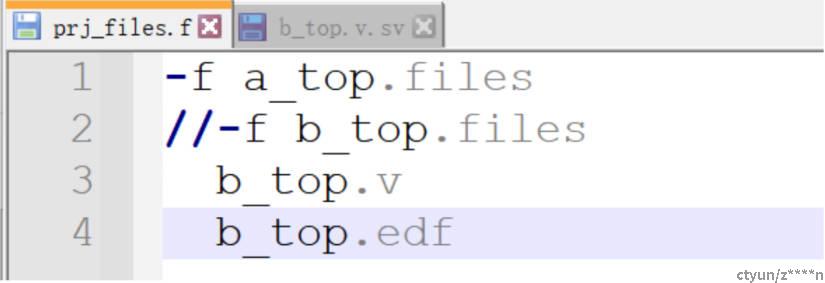

综合时B_top模块在Project_top中只保留B_top.v的接口和B_top的网表文件,B_top模块下的其他文件不用添加。工程文件如下:

B_top模块没有修改,模块代码在上一级中是以空壳形式存在(即只有顶层代码)。