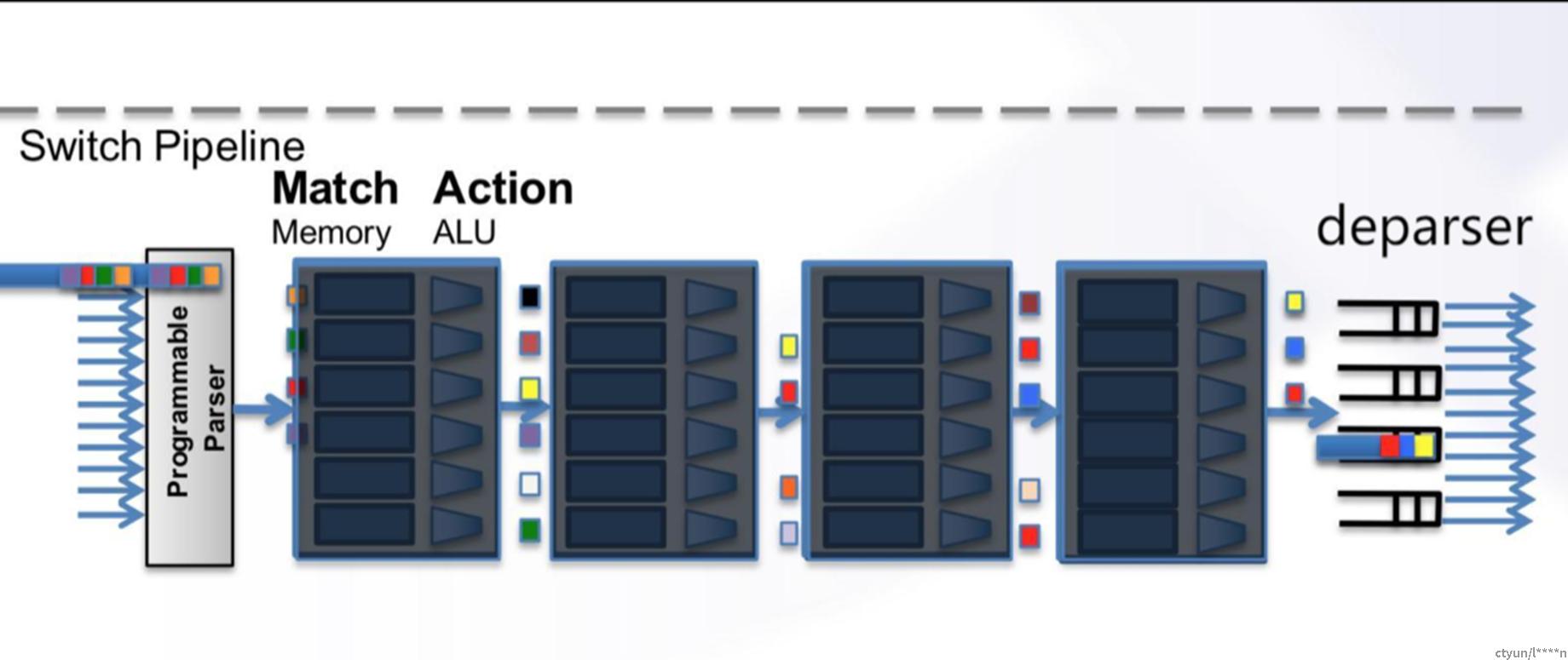

TOFINO 是Intel 旗下的一款流水线结构的芯片,有一定的流程可编程控制的Asic 芯片,由于有一定的可编程能力,包含4 条独立的 Pipe Line。

Pipe Line由 Parser MAUx 12 DeParser 三个处理模块组成。

1. Parser

主要功能是负责报文解析,报文头结构和Meta 结构的定义定义和报文头信息提取。

报文本身是不可以访问的,只有把信息提取到Meta 中在后续处理流程才可以访问。

提取的信息存放到PHV (Paket Header Vector) 数据在报文生命周期中可用。

PHV 资源4096 bit, 每个MAU 都存在一份。分为3种位宽的224 个Container

64 x 8 bit Container

96 x 16 bit Container

64 x 32 bit Container

T-PHV 是节约资源设计,报文头信息中不需要使用的,通过lookup_ahead 方法跳过的报文头信息存储到T-PHV ,是PHV 的一半 2048 bit/112 Container,全芯片一份。

Parser 解析报文是靠TCAM 匹配实现,最大支持256 条。

2. Match Action Unit(MAU)

12 MAU Per PipeLine

MAU 为主要的业务处理单元,每个MAU 称为一个 Stage.

在MAU 内部是通过 Tables Match + Action 来处理业务

用户通过配置 Tables 和 编写 Action处理代码来实现业务的处理。

根据MetaData 组织Table Key 执行查表动作,查到的Data 作为Action 的输入参数,执行Action 动作。一个Table entry 可以定义多个Action 动作,Selector 可以根据 MetaData 选择执行的动作。

一个MAU 可同时处理两个报文

一个上行报文, 一个下行报文

单个MAU最多可查16 次表,

16次SRAM或 8次TCAM

MAU 所有资源上下行共享。

表项存储的载体:

SRAM, TCAM

SRAM:

SRAM Block: 128 x 1024 bits.

80 SRAM Block Per MAU (10Mbit)

12 MAUs Per PipeLine (120 Mbits)

4 PipeLine 480 Mbits

SRAM 按功能可存储exact match 表, counter,meter,register.

按128bit 一个Entry计算, 单个MAU 最大存 8万个 Entry 表项。

12 个MAU 最大放 96 万个 Entry。

TCAM:

TCAM Block: 44 x 512 trits (22 Ktrits).

24 TCAM Block Per MAU (528 Ktrits)

12 MAUs Per PipeLine (6.1875 Mtits)

4 PipeLine 24.75 Mbits

TCAM 一般存储LPM, Ternary, range 匹配表。

1 entry最小 40 + 44*N bit 。

单个MAU 最大支持 6K entry;

12 个MAU 最大支持 72K entry;

指令数:

每个MAU 最大可存储 32 个 VLIWS

每个VLIW 最大可存储 224 个Instruction

每个MAU 指令数 32*224 = 7168

指令操作数没有依赖关系的可以并行处理

Meters:

Meters 占用的资源是SRAM (10Mbit per MAU)

全部占用的话最大可达 4W 个Meters 每个MAU。

Direct Meters: 单独CAR ,独占一份资源。

InDirect Meters: 共享CAR, 表中存储Index, 可多个共享一个

Index,共同使用一份资源。

由于Tofino 使用的是P4《P4: Programming Protocol-Independent Packet Processors》语言编程,大家习惯性得把TOFINO 芯片叫成P4 芯片。

P4是一种高级语言,协议无关的数据面包处理编程语言有如下特点:

Reconfigurability in the field 现场可重构性:一旦交换机被部署,程序员应该能够改变其处理数据包的方式

Protocol independence 协议无关性:交换机不应绑定到任何特定的网络协议

Target independence 目标无关性:程序员应该能够独立于底层硬件的细节描述包处理功能

常见的Tofino有多款型号如下:

1.型号 Tofino1

工艺: 16nm

6.5Tbps 单芯片转发新能

SerDes 256 * 25GE

数据转发通路支持端口

64 X 100GE/40GE

128 X50GE/40GE

256X25GE/10GE

CPU 通路接口

PCIe Gen2 x4/x2/x1

CPU Eth 1X100GE/40GE

2X50GE/40GE

4X1/2.5/10/25GE

报文缓存 22MB

1.型号 Tofino2

12.9 Tbps 单芯片转发新能

SerDes 256 * 56GE

数据转发通路支持端口

32 X 400GE

64 X 200GE

128 X 100GE

256X50GE/25GE/10GE

CPU 通路接口

PCIe Gen3 x4/x2/x1

CPU Eth 1X100GE/40GE

2X50GE/40GE

4X1/2.5/10/25GE

报文缓存 64MB